HBM 概述

HBM(High Bandwidth Memory)是一种由AMD和SK hynix联合开发的创新3D堆叠DRAM技术。该技术通过将多层DRAM芯片垂直堆叠,并利用高带宽的串行接口实现与GPU或CPU的直连,从而提供远远超越传统DRAM的带宽和容量。高带宽内存(HBM)它象征着内存技术的革命性跨越,尤其在高性能计算(HPC)、人工智能(AI)、数据中心和高端游戏等领域。

Memory 进化史

内存技术从早期的静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)发展至今,经历了多个关键阶段:

SRAM 与 DRAM 的诞生 :SRAM 凭借高速访问特性适用于缓存场景,而 DRAM 因高存储密度和成本效益成为主内存的首选。

同步动态随机存取存储器(SDRAM) :为缩小内存与 CPU 速度差距而引入,实现单时钟周期内数据读写。

双倍数据率同步动态随机存取存储器(DDR SDRAM) :利用时钟上升沿和下降沿传输数据,使数据传输速率翻倍。

多倍数据率技术的发展 :从 DDR 到 DDR2、DDR3、DDR4直到DDR5,内存数据传输速率持续提升,功耗和成本效益不断优化。

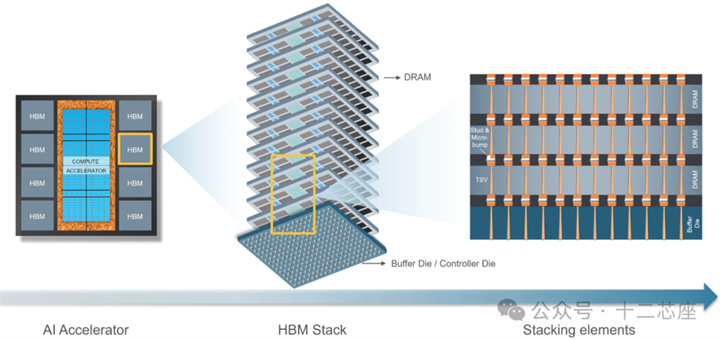

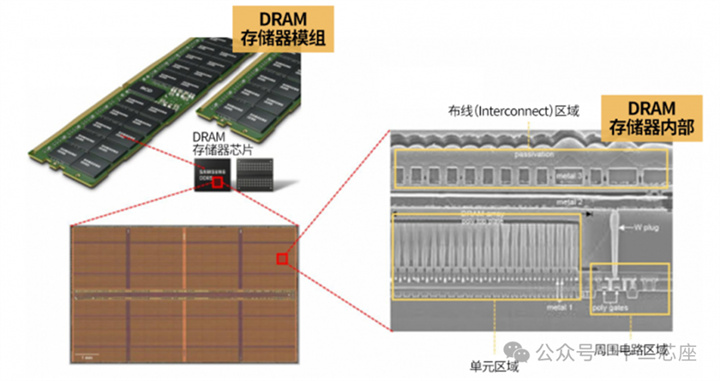

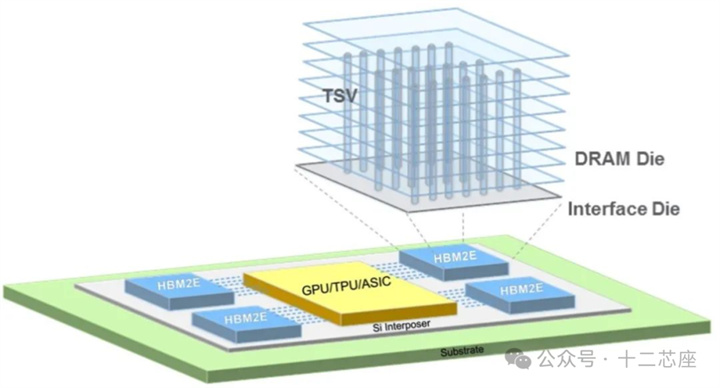

HBM 原理

HBM 原理HBM 的核心在于独特的 3D 堆叠架构和 TSV(Through - Silicon - Via)技术:

3D 堆叠架构 :垂直堆叠多个 DRAM 芯片层,增加单位面积内存容量,各层 DRAM 通过微凸点与逻辑芯片相连。

TSV 技术 :在硅芯片中垂直贯穿导电通路连接不同层次电路,减少芯片间连接长度和电阻。

高带宽串行接口 :与传统并行接口相比,串行接口在更少引脚数量下实现更高数据传输速率。

HBM优势

高带宽 :满足高性能计算需求,带宽远超传统 DRAM。

高容量 :3D 堆叠技术在相同芯片面积内集成更多 DRAM 层,提供更大内存容量。

低功耗 :垂直堆叠结构减少数据传输距离,TSV 技术也有助于降低功耗。

小尺寸 :3D 堆叠设计使内存模块尺寸大幅减小,利于系统紧凑设计。

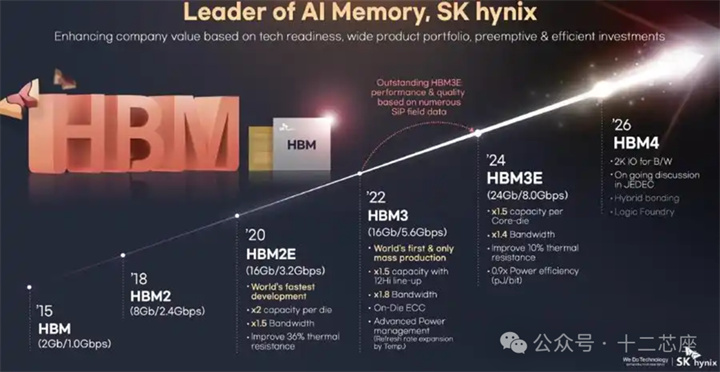

HMB技术发展历程

2013年:

AMD 与 SK hynix宣布合作开发 HBM 技术。

2015 年:

HBM 技术的开端,当时的带宽为 1.0Gbps,容量为 2Gb。

2018年:

容量提升至 8Gb,带宽升至 2.4Gbps。它是世界上发展最快的版本,相比前代,每芯片容量翻倍、带宽提升 1.5 倍,热阻也提升了 34%。

2020年:

容量和带宽达到 16Gb 和 3.2Gbps。其在速度和容量上均有显著增强。

2022年:

带宽提升至 5.6Gbps,SK 海力士实现了全球首次量产。该技术具备 1.5 倍的容量提升、1.8 倍的带宽提升、1.2Hi 连接,还采用了芯片上芯片(On-Die)、先进电源管理(通过 Temp.管理)等技术。

2024年:

容量达到 24Gb,带宽高达 8.0Gbps。其每芯片容量提升 1.5 倍,带宽提升 1.4 倍,并且热阻改善了 10%,能效达到 0.9x(pJ/bit)。

2026年:

计划在 2026 年推出 HBM4 技术,将在 JEDEC 标准下进行讨论,采用混合键合技术以及逻辑晶圆厂生产。

总结

高带宽内存(HBM)作为现代计算领域的一项革命性技术,凭借其独特的 3D 堆叠架构和 TSV 技术,在性能、容量、功耗和尺寸等方面实现了全方位突破。自 2013 年问世以来,HBM 经历了多次迭代升级,从最初的 1.0Gbps 带宽到如今的 8.0Gbps,不仅推动了高性能计算、人工智能、数据中心等领域的快速发展,也为未来的技术演进奠定了坚实基础。展望未来,随着 HBM4 技术的逐步落地,这一技术将继续引领内存发展的潮流,为人类社会的智能化进程注入更强动力。