一、晶圆翘曲的成因

晶圆翘曲并非单一因素所致,而是在热、机械、化学多物理场耦合作用下,由材料本征属性与复杂制程相互作用引发的宏观形变。其核心是应力生成大于结构刚度所能容纳的极限。

1、材料本征属性失配是物理基础

• 热膨胀系数失配:这是产生热应力的根本。硅(~2.6 ppm/°C)、封装聚合物(如EMC, 7-20 ppm/°C)、铜(~17 ppm/°C)等材料在温度循环(如回流焊峰值260°C以上)中膨胀与收缩不同步,产生巨大的界面剪切应力与整体弯曲力矩。在2.5D/3D封装中,硅中介层与有机基板间的CTE鸿沟是翘曲的主要来源。

• 模量(刚度)失配:高模量材料(如硅、金属)与低模量材料(如聚合物、胶材)在受力时变形不协调,导致应力在界面处集中。例如,刚性芯片被柔软的底部填充料包围,在温度变化时,填充料的变形会受到芯片制约,反之亦然。

• 材料属性随工艺演变:高分子材料(如PI、EMC)在固化过程中的体积收缩、固化度变化及玻璃化转变温度都会动态改变其模量与CTE,使得应力状态极为复杂。

2、先进制程是应力的直接引入与放大器

• 薄膜沉积的固有应力:化学气相沉积薄膜(如SiN、SiO₂)具有本征应力,源自薄膜生长过程中原子/分子的非平衡态堆积,可分为张应力和压应力,数值可达数百兆帕至吉帕量级。这些应力的逐层累积是晶圆在未封装前就发生翘曲的重要原因。

• 图形化与异质集成破坏结构完整性:深硅刻蚀形成TSV、激光开孔等工艺在晶圆中制造了应力集中点。金属布线(RDL)带来的局部刚度增强效应与介质层区域形成鲜明对比,导致“景观式”应力分布。3D堆叠中的混合键合或微凸块连接,引入了新的、难以预测的界面应力。

• 晶圆薄化与临时键合的力学挑战:将晶圆研磨至100µm以下(甚至25µm)使其抗弯刚度呈厚度立方关系急剧下降,对应力极为敏感。临时键合胶在高温下的粘弹性松弛、载板与晶圆间的CTE失配,以及解键合时(无论是机械剥离、激光烧蚀还是热滑移)的能量冲击,都是高风险的翘曲诱发环节。

3、设计拓扑结构决定了应力分布形态

• 几何非对称性:几乎所有先进封装结构都是非对称叠层(如正面有多层RDL和凸块,背面仅有薄钝化层)。这使得结构的中性面严重偏离其几何中面,导致在温度变化时,微小的应力差也会被放大为显著的弯曲变形。

• 图案密度不均匀性:芯片核心区的金属密度(>80%)与外围及切割道区域(<10%)差异巨大,导致晶圆局部区域的有效CTE和等效模量不同。这种“马赛克”式的材料分布会引发复杂的、非球面化的高阶翘曲模式,给光刻全局调平带来极大挑战。

二、翘曲的影响

翘曲的影响是全流程和链式反应的:

• 制程可行性风险:在光刻环节,过大的翘曲会超出焦深容限,导致图形失真或无法同时曝光。在键合与贴装环节,翘曲使共面性变差,导致微观凸块连接压力不均、产生空洞或桥接,直接影响电气连接可靠性。

• 机械完整性风险:翘曲的晶圆在传输、研磨、切割过程中易发生碎裂。较大的残余应力也是芯片在后续模块组装或终端使用中发生开裂、分层的潜在根源。

• 长期可靠性风险:翘曲是封装体内部存在巨大残余应力的外在表现。这些应力在产品的温度循环、功率循环服役条件下会成为疲劳裂纹萌生与扩展的驱动力,加速焊点失效、介电层破裂等故障。

三、系统性改善对策

现代先进封装的翘曲管理已从后期的工艺修补,转变为贯穿设计、材料、制程、仿真全链条的主动应力工程。

1、材料层面的创新与选择

• 开发先进封装专用材料:研发低收缩率、低模量、且CTE可调的底部填充料、模塑料和介电材料。例如,在环氧树脂中引入纳米二氧化硅或弹性体微球,在降低CTE的同时保持一定的韧性以吸收应力。

• 实施应力匹配设计:在堆叠设计中有意识地采用CTE梯度过渡材料,例如在芯片与高CTE基板之间插入一层中等CTE的中间层,以缓和应力突变。

• 薄膜应力精确调控:通过改变沉积工艺参数(如温度、压力、功率、气体比例)或采用多层应力补偿结构(如压应力膜与张应力膜交替),将薄膜堆叠的总应力控制接近于零。

2、结构与设计层面的优化

• 强制对称化设计:在完成正面制程后,于晶圆背面沉积主动应力平衡层。该层材料(如特定应力的SiN或金属层)的厚度与应力经过精确计算,旨在产生一个反向力矩,将翘曲“拉平”。这是处理高阶翘曲最有效的设计手段之一。

• 布局密度均匀化:在切割道和低密度区域系统性地插入虚拟金属图案,使整个晶圆表面的金属/介质分布尽可能均匀,从而消除因图案密度差异引起的局部应力。

• 载体与中介层的战略选择:对于高精度2.5D封装,优先选用与芯片CTE近乎匹配的硅或玻璃中介层,而非传统有机基板,从载体端大幅降低热失配。

3、制程工艺层面的精细控制与创新

采用 “研磨+化学机械抛光+湿法/干法刻蚀” 的组合薄化工艺,去除机械研磨造成的损伤层,获得低应力、光滑的背面。

• 优化临时键合系统:开发 “刚性载板+低模量、高温稳定的释放胶” 组合,在制程中提供刚性支撑,同时在解键合时能温和、均匀地释放应力。

• 低温与低温工艺:大力发展低温键合(如表面活化键合)、低温沉积工艺,从根本上减少热应力来源。

• 引入应力弛豫步骤:在关键的高应力制程(如薄膜沉积、高温固化)后, strategically 插入退火工艺,使材料内部的原子/分子有足够动能进行重排,释放部分内应力。

• 先进薄化与支撑技术:

采用 “研磨+化学机械抛光+湿法/干法刻蚀” 的组合薄化工艺,去除机械研磨造成的损伤层,获得低应力、光滑的背面。

优化临时键合系统:开发 “刚性载板+低模量、高温稳定的释放胶” 组合,在制程中提供刚性支撑,同时在解键合时能温和、均匀地释放应力。

4、预测与监控层面的数字化赋能

• 基于仿真的预测性设计:在产品研发初期,利用有限元分析等计算工具,建立包含所有材料非线性(温度相关CTE、模量)、固化收缩、粘弹性等行为的精细模型。通过虚拟“试错”,提前预测翘曲趋势,优化堆叠顺序、材料选择和结构尺寸,实现“首次即正确”。

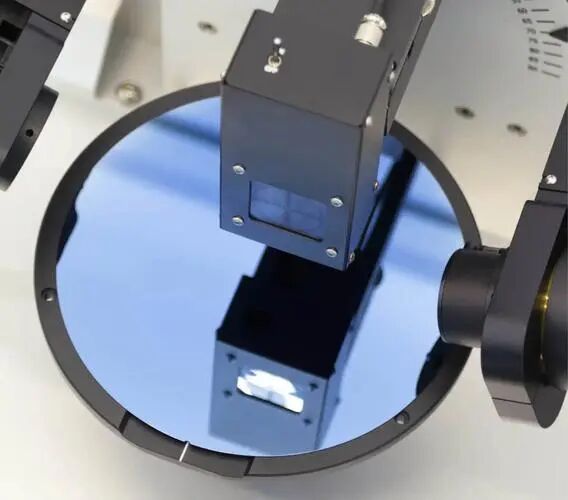

• 全流程在线监控与反馈控制:在生产线上关键节点(如薄化后、键合后)部署自动化的翘曲测量设备,建立翘曲数据图谱。通过与工艺参数的关联分析,实现动态工艺窗口调整和前馈/反馈控制,确保翘曲始终处于受控范围。

四、总结与前沿展望

晶圆翘曲是先进封装向更高集成度、更薄化、异质集成发展的必然伴生挑战。解决之道已从单一的工艺调整,演变为一个涉及材料科学、固体力学、工艺工程和计算科学的综合性学科。

前沿研究方向包括:

• 智能材料:开发能感知并主动补偿应力的自适应材料。

• 原子尺度模拟:从更微观层面理解界面应力的产生与演化机制。

• AI/ML驱动的工艺优化:利用机器学习算法,在海量的工艺参数与翘曲数据中寻找最优解,实现自适应工艺控制。

本质上,对翘曲的有效管控能力,已成为衡量一家企业或一个技术平台能否实现下一代先进封装(如3D SoIC、芯粒异构集成)量产的核心竞争力之一。