在追求更高性能、更小尺寸和更低功耗的半导体行业浪潮中,三维集成技术已成为推动摩尔定律持续前行的关键路径。在众多3D封装方案中,根据集成方式和工艺顺序的不同,衍生出了几种主流的先进封装技术,它们以其独特的结构和流程,共同支撑起现代异构计算的宏伟蓝图。

PoP:Package-on-Package Assembly/堆叠封装

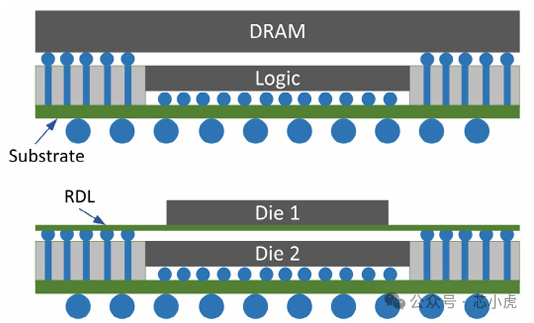

实现 3D 集成的较简单方案之一,是将已完成封装的芯片进行堆叠。这类方案的技术名称中通常包含 “PoP”(即 “封装堆叠”)。该技术的一个典型应用场景是将 DRAM 芯片堆叠在逻辑芯片上方,台积电(TSMC)的 InFO 封装技术中,就包含此类堆叠方案。

CoW:Chip on Wafer Assembly/晶圆级芯片集成

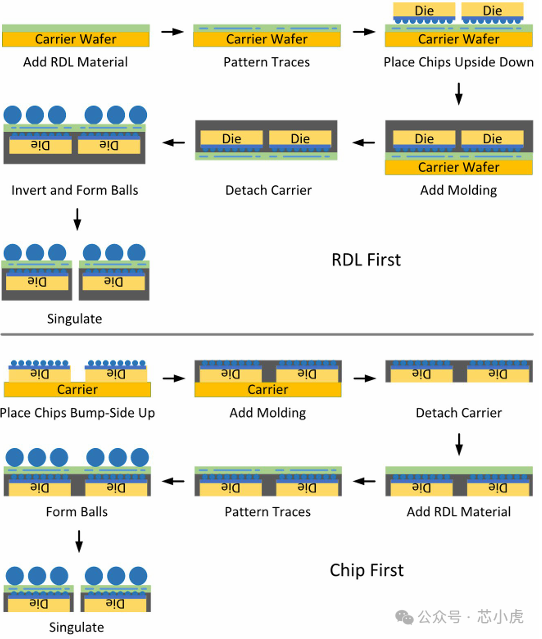

在封装中实现芯片互连的早期方案之一,是采用晶圆作为载体,并在其上制作重布线层(RDL),台积电将该技术品牌化为 “CoW”(晶圆级芯片集成)。以下介绍两种典型的组装流程方案:

第一种方案的流程为:先在载体晶圆上制作重布线层(RDL),再将预先切割好的芯片(焊凸朝下)放置在载体上;随后对芯片进行塑封,形成 “重构晶圆”(reconstituted wafer);之后移除载体晶圆,制作焊球,最后对重构晶圆进行切割( singulate),得到独立封装体。

另一种方案的流程则不同:先将芯片倒扣在载体晶圆上,再进行塑封;移除载体晶圆后,制作重布线层与焊球;最后对重构晶圆进行切割,完成封装。

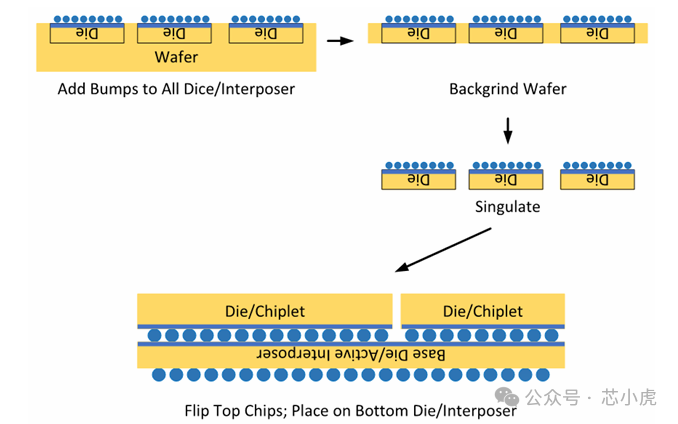

英特尔(Intel)的 Foveros 工艺是该技术的另一变体,主要用于实现两颗芯片(或一颗芯片与一个有源中介层)的面对面键合。其中,下方芯片需朝上放置,并通过硅通孔(TSV)与基板实现连接。

加入中介层(Adding Interposers)

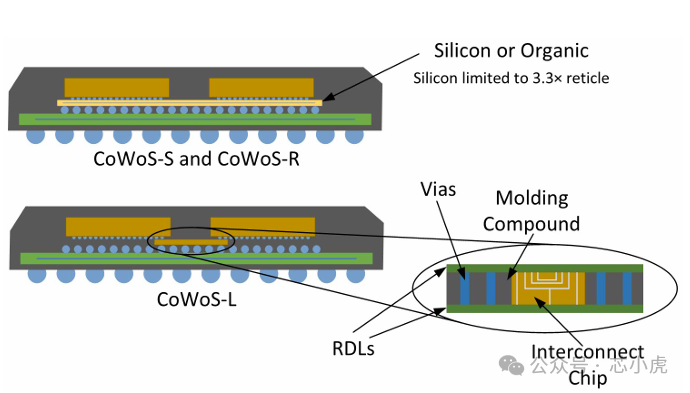

前文介绍的方案仅通过重布线层(RDL)实现信号向焊球的布线。若在封装中加入中介层,则能进一步提升布线灵活性。台积电的 CoWoS(晶圆级系统集成封装)是最知名的案例之一,该技术根据中介层的类型分为三个变体:

CoWoS-S:采用硅中介层;

CoWoS-R:采用有机材料制作重布线层(无独立中介层,以有机 RDL 替代中介层功能);

CoWoS-L:采用小型芯片作为 “布线载体”—— 其结构类似硅桥(silicon bridge),但额外具备通向基板的通孔(vias),可直接与基板连接。

总结:

从简单的封装堆叠(PoP),到以晶圆为载体的芯片集成(CoW),再到引入中介层以极致发挥布线潜力的CoWoS技术,先进封装的演进清晰地展示了一条从二维到三维、从单一到异构的系统级整合路径。这些技术不仅突破了传统封装的物理限制,更通过灵活的芯片组合,为未来算力提供了无限可能。它们共同构成了半导体产业的下一个前沿,预示着电子系统性能与集成度的新纪元。